## Hardware synthesis in ForSyDe

The design and implementation of a ForSyDe-to-VHDL Haskell-embedded compiler

## ALFONSO ACOSTA

Master's Thesis at KTH/ICT/ECS Supervisor: Ingo Sander Examiner: Ingo Sander Stockholm, June 2007

Copyright © 2007 by Alfonso Acosta <alfonso.acosta@gmail.com>

This work is licensed under the Creative Commons Attribution-No Derivative Works 3.0 License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nd/3.0/ or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

## Abstract

The ForSyDe (*Formal System Design*) methodology is targeted at modelling systems, with the goal of using a high level of abstraction in the speci cation of its models.

Although it is a general system modelling methodology, the initial scope of ForSyDe has speci-cally been *Synchronous Systems* (systems in which a global clock is used to synchronize the di-erent parts of the system). A well-known type of such system is synchronous hardware, which is the main subject of this thesis. A synchronous system in ForSyDe is based on the concept of *processes* which "map input signals onto output signals".

Currently, the software implementation of ForSyDe is based upon the Haskell programming language. The designer speci es the system model in Haskell as a network of cooperating process constructors with the assistance of the ForSyDe Library.

Until now, there has not been an automated way to synthesize ForSyDe models (i.e. generate an equivalent low-level implementation from which to build real hardware). However, as a result of this thesis, hardware synthesis is now a feature of ForSyDe, enabling ForSyDe designs to nally reach silicon. That is possible thanks to the development of a ForSyDe-to-VHDL compiler. By using this compiler, a ForSyDe model can be rst translated to synthesizable VHDL93 (one of the two most common hardware design languages) and then, the designer can use any of the existing VHDL-tools to synthesize the model.

This thesis report is aimed at documenting the background, design, implementation and use of the compiler.

## Acknowledgements

There are many people who in one form or another contributed to the work described in this thesis.

I would like to thank Ingo Sander, my supervisor, for his flexibility and trust during the thesis. He has always been positive about my, sometimes not-so-frequent and too extensive, thesis status reports. I would also like thank him and give him credit for kindly letting me use some of the gures of his PhD thesis [1].

I am also tremendously thankful to the Haskell community, which has proven to be, by far, the most friendly, helpful and smart programming community I have ever been involved with. Special thanks go to the guys at the #haskell IRC channel at freenode.net and the haskell-cafe mailing list. There are too many community-people to thank but I would like to speci cally mention Oleg Kiselyov for his selfless help \_ xing and designing the compiler's typechecker.

Koen Claessen gave me access to Lava's sourcecode, which turned to be essential during the development of the compiler. Without Lava, the compiler would have been totally di erent and perhaps even unfeasible.

Last but not least, I would like to thank Iván Pérez and Miguel Jiménez who helped reviewing parts of the thesis, my parents, for their support, whithout which I would not had been able to spend my last two academic years in Stockholm and nally, all the Erasmus students which turned my stay in Sweden into one of the best experiences of my life (they know who they are).

Stockholm, June 2007

Alfonso Acosta

## Preface

This thesis report is aimed at documenting the background, design, implementation and use of a compiler which translates ForSyDe (*Formal System Development*) speci cations into VHDL93 [2] synthesizable code.

The current implementation of ForSvDe, in which the compiler was embedded, is written in the Haskell [3] programming language. That means the compiler has unavoidably been coded in the same language. For that reason, it will be assumed that the reader of this report is fluent in Haskell. Introducing the reader to Haskell is out of the scope of the present text. There are many resources from where to acquire the necessary knowledge. Just to mention three of them, A Gentle Introduction to Haskell [4] is available online at no cost and is supposed to be a friendly text for the newcomers, Thomson's book Haskell: the Craft of Functional Programming [5] on the other hand is longer but covers the language in greater detail and nally the upcoming *Real-World Haskell* book<sup>1</sup> [6] will be freely available online and will help to get involved with serious real-world Haskell code and practical Haskell programming. Mastering Haskell is not a prerequisite to understand the overall content of the thesis. However, wide Haskell programming-experience and familiarity with its common extensions would de nitively be useful (and is probably needed) to comprehend the compiler's design and implementation details.

In addition, it will be assumed that the reader is familiar with digital hardware design and development through HDLs (*Hardware Design Languages*) or, in the worst case, understands the concepts behind it. This prerequisite is weaker than knowing Haskell, since speci c knowledge of VHDL is not essential to read the report. However, being aware of the purpose of an HDL is vital to understand the goals which were achieved.

This thesis report is divided in ve chapters:

**Chapter 1** introduces the reader to ForSyDe and the thesis goals. It also introduces the concept of Embedded DSL (*Domain Specific Language*) which is essential to understand ForSyDe's implementation.

<sup>&</sup>lt;sup>1</sup>Not ready by the time of writing this preface.

**Chapter 2** is targeted at comparing ForSyDe with Lava, a successful Haskell-embedded HDL (*Hardware Description Language*) and veri cation environment. The comparison was written before developing the compiler, in order to acquire the necessary background in the *Hardware Design and Functional Languages* research eld, hoping to be able to later reuse previous research results and provide ForSyDe's compiler with state-of-the-art features.

ForSyDe's translator to VHDL turned out to be strongly influenced by Lava. As a result of the comparison, the compiler is intended to inherit Lava's virtues and overcome some of its problems such as its current lack of component reusability on the compiler-level. **Chapter 3** describes the design of the compiler and the motivation behind it whereas **Chapter 4** is targeted at the end-user and contains a tutorial to help getting familiar with the tool and its API.

Finally Chapter 5 closes the thesis analyzing its results and outlining potential improvements and further work.

As an add-on, **appendix A** has been written with future developers in mind. They will surely nd this appendix useful to get familiar with the compiler's implementation in rst instance, and later improve it or extend it at will (the sources are available under the BSD licence at http://www.imit.kth.se/info/FOFU/ForSyDe/HDForSyDe/).

# Contents

| A             | bstra  | $\operatorname{ct}$                                        | i            |

|---------------|--------|------------------------------------------------------------|--------------|

| A             | cknov  | wledgements                                                | iii          |

| Pı            | reface | 5                                                          | $\mathbf{v}$ |

| Co            | onten  | ıts                                                        | vii          |

| $\mathbf{Li}$ | st of  | Figures                                                    | x            |

| $\mathbf{Li}$ | st of  | Abbreviations                                              | xi           |

| 1             | Intr   | oduction                                                   | 1            |

|               | 1.1    | What is ForSyDe?                                           | 1            |

|               |        | 1.1.1 Why a higher abstraction level?                      | 1            |

|               |        | 1.1.2 ForSyDe's design flow                                | 2            |

|               | 1.2    | ForSyDe's implementation                                   | 5            |

|               |        | 1.2.1 Embedded DSLs                                        | 6            |

|               |        | 1.2.2 ForSyDe's Library                                    | 6            |

|               | 1.3    | Thesis scope and goals                                     | 7            |

| <b>2</b>      | Lava   | a vs ForSyDe                                               | 9            |

|               | 2.1    | Introduction                                               | 9            |

|               | 2.2    | Design flow                                                | 10           |

|               | 2.3    | Backends                                                   | 12           |

|               | 2.4    | Language features                                          | 13           |

|               |        | 2.4.1 Representing a circuit in a pure functional language | 16           |

|               | 2.5    | Lava and ForSyDe in practice                               | 20           |

|               | 2.6    | Conclusions                                                | 24           |

| 3             | Des    | ign of the compiler                                        | <b>25</b>    |

|               | 3.1    | Design alternatives                                        | 25           |

### Contents

|              |     | 3.1.1 Why an embedded compiler?                                                                                                     | 26        |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|-----------|

|              | 3.2 | Di erences with Lava's implementation                                                                                               | 27        |

|              | 3.3 | HDSignal: The Hardware Description Signal                                                                                           | 29        |

|              | 3.4 | HDFun: the Hardware Description Function                                                                                            | 30        |

|              |     | 3.4.1 Introduction to Template Haskell                                                                                              | 30        |

|              |     | 3.4.2 HDFuns in practice                                                                                                            | 31        |

|              | 3.5 | Controlling polymorphism: the HDPrimType type class                                                                                 | 32        |

|              | 3.6 | Integration with ForSyDe's Library                                                                                                  | 33        |

|              | 3.7 | Improvements over Lava's original design                                                                                            | 34        |

|              |     | 3.7.1 Ports                                                                                                                         | 34        |

|              |     | 3.7.2 Hierarchical structures                                                                                                       | 36        |

| <b>4</b>     | Use | r's tutorial                                                                                                                        | 39        |

|              | 4.1 | Prerequisites                                                                                                                       | 39        |

|              | 4.2 | Identity system                                                                                                                     | 39        |

|              |     | 4.2.1 Compiling the model                                                                                                           | 42        |

|              | 4.3 | A more complex system                                                                                                               | 42        |

| <b>5</b>     | Con | clusions and further work                                                                                                           | 47        |

|              | 5.1 | Conclusions                                                                                                                         | 47        |

|              |     | 5.1.1 Goal analysis                                                                                                                 | 48        |

|              | 5.2 | Further work                                                                                                                        | 50        |

| $\mathbf{A}$ | Hac | ker's guide to the compiler                                                                                                         | <b>53</b> |

|              | A.1 | 1                                                                                                                                   | 53        |

|              | A.2 | Compiler modules overview                                                                                                           | 54        |

|              |     | A.2.1 Core modules                                                                                                                  | 54        |

|              |     | A.2.2 Miscellaneous auxiliary functions and types                                                                                   | 56        |

|              |     | A.2.3 Ports, Blocks and Block Instances                                                                                             | 57        |

|              |     | A.2.4 Backends                                                                                                                      | 57        |

|              |     | A.2.5 Integration with ForSyDe                                                                                                      | 58        |

|              | A.3 | Recipes to extend the compiler                                                                                                      | 59        |

|              |     | A.3.1 Adding support for new types of signal values                                                                                 | 59        |

|              |     | A.3.2 Treating more ForSyDe processes as primitives                                                                                 | 60        |

|              |     | A.3.3 Extending HDFun's Haskell-syntax subset                                                                                       | 60        |

|              |     | A.3.4 Adding support for new functions within HDFuns                                                                                | 60        |

|              |     | A.3.5 Adding a new backend                                                                                                          | 61        |

|              | A.4 | Improving the source code                                                                                                           | 62        |

| Б            |     |                                                                                                                                     |           |

| В            |     | $ mples \\ plus1 \dots \dots$ | <b>63</b> |

viii

## Contents

|             | Plus1.hs             |    |

|-------------|----------------------|----|

|             | RTL model of $plus1$ |    |

| C ForSyDe's | s VHDL Library       | 67 |

| C.1 forsy   | de.vhd               | 67 |

# List of Figures

| 1.1 | ForSyDe's design flow                      | 2 |

|-----|--------------------------------------------|---|

| 1.2 | Process                                    | 3 |

| 1.3 | A Synchronous system model in ForSyDe      | 3 |

| 1.4 | Primitive and derived process constructors | 1 |

| 1.5 | A simple speci cation model                | 5 |

| 1.6 | ForSyDe's Library                          | 3 |

| 2.1 | Lava's design flow                         | L |

| 2.2 | ForSyDe's design flow                      | Ĺ |

| 3.1 | <i>plus1</i>                               | ) |

| 3.2 | Hierarchical structures                    | 5 |

| 4.1 | Identity system                            | ) |

| 4.2 | A more complex system                      | 3 |

| A.1 | Compiler modules' dependency graph         | 5 |

| B.1 | RTL model of $plus1$                       | 5 |

# List of Abbreviations

| ADT     | Abstract Data Type                 |

|---------|------------------------------------|

| API     | Application Programming Interface  |

| AST     | Abstract Syntax Tree               |

| BSD     | Berkeley Software Distribution     |

| CAD     | Computer-Aided Design              |

| DSL     | Domain Speci c Language            |

| EDSL    | Embedded DSL                       |

| ForSyDe | Formal System Design               |

| FPGA    | Field-Programmable Gate Array      |

| GHC     | Glasgow Haskell Compiler           |

| HDL     | Hardware Description Language      |

| IO      | Input Output                       |

| IRC     | Internet Relay Chat                |

| MPTC    | Multi-parameter Type Class         |

| RTL     | Register Transfer Level            |

| ST      | State Transformer                  |

| TH      | Template Haskell                   |

| VHDL    | VHSIC HDL                          |

| VHSIC   | Very-High-Speed Integrated Circuit |

| VLSI    | Very-Large-Scale Integration       |

| XML     | eXtensible Markup Language         |

| YACC    | Yet Another Compiler Compiler      |

## Chapter 1

## Introduction

This chapter is aimed at introducing the reader to ForSyDe and the goals of this thesis.

The main intention of this introduction is to bring the reader to understand ForSyDe in a friendly way. Thus, when necessary, clarity was chosen over formalisms. If a complete and more accurate description of ForSyDe is required, please refer to [7] and [1].

## 1.1 What is ForSyDe?

ForSyDe, which stands for Formal System Design, is a system design methodology "which has been developed with the objective to move system design to a higher level of abstraction and to bridge the abstraction gap by transformational design refinement" [1].

ForSyDe targets system modelling in general. However, by the time of writing this thesis, the methodology only covers *Synchronous Systems* (systems in which a global clock is used to synchronize the di erent parts of the system). A well-known type of such system is synchronous hardware, which is the main topic of the thesis.

### 1.1.1 Why a higher abstraction level?

The systems designed nowadays, with microelectronic systems as a particular example, are tremendously complex due to the increasing feature and functionality demands of the market.

Furthermore, not only designs are more complex, the aggressive competitivity of industry requires companies to also shorten the time-to-market of their products, a ecting the development cycle.

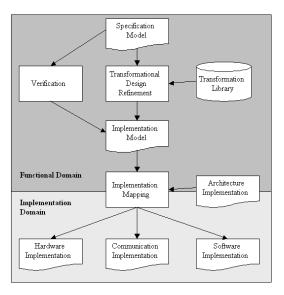

Figure 1.1: ForSyDe's design flow

For the reasons mentioned above, previous techniques, such as the RTL (*Register Transfer Level*) languages developed during the 80's (mainly Verilog and VHDL) give too much detail for the designer to handle. In other words, the level of abstraction of those techniques is too low and hinders the design process. As a result, a big e ort was devoted to raise the abstraction level of design automation tools, resulting in the *System-level Design* research eld, to which ForSyDe belongs.

### 1.1.2 ForSyDe's design flow

#### 1.1.2.1 Specification model

Figure 1.1 summarizes ForSyDe's design flow. The design is initiated by writing its *specification model*.

As it was previously stated, ForSyDe currently only covers *Synchronous Systems*. For that reason, the speci cation model follows a *synchronous model of computation*. The *specification model* of a synchronous system in ForSyDe is based on the concepts of *synchronous signal* and *process*:

• A synchronous signal is a general term in Computer Science and the Telecommunications eld. It can be de ned as an entity transmitting information in a synchronous manner. That is, the transmission of information is arbitrated by a clock and remains static during each clock period, only allowed to change between periods.

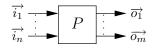

Figure 1.2: Process

Figure 1.3: A Synchronous system model in ForSyDe

For SyDe uses the following notation to express a synchronous signal  $\overrightarrow{s}$ ,

$$\vec{s} = \ll v_0, v_1, v_2, \dots \gg$$

where  $v_i$  indicates the value of the signal during period *i* of the clock.

From now on, this report will use the terms *signal* and *synchronous signal* equivalently.

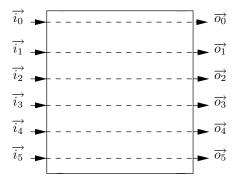

• The meaning of **process** is speci c to ForSyDe and is represented in Figure 1.2. A process can be de ned as a computational entity which takes  $n \in \mathbb{N}_0$  synchronous input signals, might process them and then produce  $m \in \mathbb{N}_0$  synchronous signals as output.

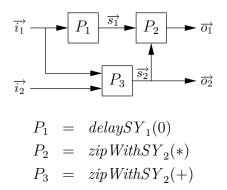

A synchronous system in ForSyDe is modelled as a network of interconnected cooperating processes which are in charge of taking the input signals of the system, process them and nally produce its output signals. A simpli ed example can be seen in gure 1.3. As a result, writing the *specification model* consists in de ning the aforementioned process network.

The ForSyDe methodology provides a wide variety of primitive and derived process constructors (entities used to build processes) in which to base a model. Consult [1] for details on the available process constructors.

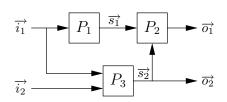

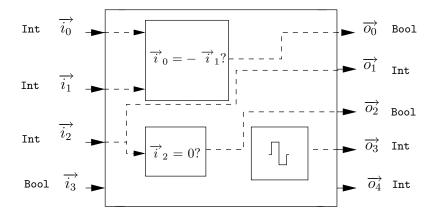

The following examples help to understand how the *specification model* is written and how processes work:

• mapSY (gure 1.4a) is a primitive process constructor aimed at processing an input signal (i) through a function (f, which must be provided to the constructor in advance) and output it for later processing by other parts of the system.

Figure 1.4: Primitive and derived process constructors

- The delaySY<sub>k</sub> primitive process constructor (gure 1.4b), on the other hand takes an initial value s<sub>0</sub> and delays a signal i by k clock periods delaySY<sub>k</sub> is useful to avoid zero-loops (known as combinational loops in the hardware world), which are not allowed in ForSyDe as it will be seen in next chapter.

- *sourceSY* (gure 1.4c) is a derived process constructor aimed at producing a custom source signal. It is derived from *delaySY* and *mapSY*.

- Figure 1.5 contains a simple speci cation model, in which the reader can see its di erent processes. It is worth to note the use of numerical signals and the  $zipWithSY_k$  process constructor, which is a generalization of mapSY for k inputs.

#### 1.1.2.2 Implementation model

The next step in the design flow is to transform the speci cation model into the *implementation model*.

The purpose of this intermediate step is to re ne the design and to add low level information details which might be needed for an e cient implementation. As it was stated before, ForSyDe's tries to to "bridge the abstraction gap by transformational design refinement", which is exactly what happens in this stage.

The initial speci cation model is re-ned by automatic *design transformation rules* which rely on the formal foundations of ForSyDe.

Figure 1.5: A simple speci cation model

Unfortunately, by the time of writing this thesis, the automatization of this stage has not yet been implemented and constitutes a tremendously complex task by itself due to the wide range of possible transformations.

### 1.1.2.3 Implementation mapping

The last stage of the design flow consists in transforming the *implementation* model into an architecture-speci c model, such as a software implementation (e.g. C, C++, ...) or hardware speci cations (e.g. VHDL, Verilog, ...) from which to synthesize hardware.

In the same way as the *design transformation rules*, the *implementation mapping* stage was not automated before this thesis was written. However, the main goal and outcome of the thesis has been to produce a compiler to translate ForSyDe speci cations into VHDL. From the VHDL model any of the available tools can be used to build or simulate real hardware, making possible to automatically synthesize ForSyDe speci cations.

## 1.2 ForSyDe's implementation

In order to use ForSyDe in practice, the designer needs a language in which to specify the model. Current implementation of ForSyDe is based on a EDSL (*Embedded Domain Specific (programming) Language*).

Figure 1.6: ForSyDe's Library

### 1.2.1 Embedded DSLs

A DSL (*Domain Specific (programming) Language*), in contrast to a generalpurpose programming language such as C, is a programming language designed for a speci c kind of task. ForSyDe is speci cally targeted at System Modelling and for that reason, the language chosen to write ForSyDe models must necessarily be a DSL.

On the other hand, an *embedded language* is a programming language which relies on an existing language, called *host language*, as opposed to the embedded language itself which is called *guest language*. In practice, the guest language is embedded by adding a library to the host language.

The main advantage of the language embedding approach is the reutilization of the syntax of the host language, its surrounding tools and documentation. Strongly-typed languages like Haskell, help embedding and are a good choice as host languages due to their encapsulation properties. However, an embedded language has, as well, many disadvantages due to the syntactical and semantical dependence on the host language.

Examples of popular EDSLs are YACC (the C-based parser generator) and EmacsLisp (used as the scripting language of the popular Emacs editor).

### 1.2.2 ForSyDe's Library

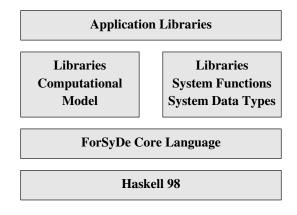

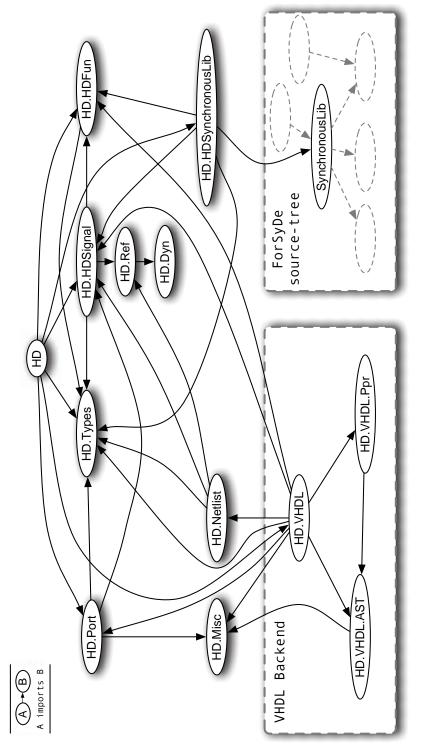

ForSyDe is implemented as a Haskell-embedded DSL. All ForSyDe's process constructors, together with other functionalities, are included in a Haskell library. Figure 1.6 illustrates the structure of ForSyDe's Library which is used by the designer to write the speci cation model in Haskell.

Choosing Haskell as the host language was not an arbitrary decision. Func-

tional languages have proven to t nicely with hardware design [8]. Even if ForSyDe is aimed at system design in general, it matches perfectly with the characteristics of Haskell:

- As it was previously described, a signal in ForSyDe is viewed as stream of values. That makes it possible to model a signal as a list, which is the main data structure of functional languages in general and Haskell in particular.

- Processes take signals as input, process them and output new signals which are later forwarded to other processes, forming a network. That ts perfectly well with functional languages. A process can be modelled as a function which makes computations over lists.

- The majority of ForSyDe's process constructors, such as *mapSY*, take functions as input. Yet again, that can be easily modelled making use of higher order functions, which are available in Haskell. Note that this reflects the initial intention of embedding ForSyDe in Haskell since its process constructors are named after widely-used higher-order Haskell functions (e.g. map, zipWith ...).

During the rest of this thesis the term ForSyDe refers indistinctively to both the methodology and its library.

## 1.3 Thesis scope and goals

The task of this master's thesis is to develop a tool that takes a ForSyDe implementation model as input and produces a hardware description in VHDL. The master's thesis must attain the following goals:

- 1) Study of ForSyDe and related work relevant to this thesis.

- 2) De nition of a relevant subset of Haskell that is accepted by the synthesis.

- 3) Development of the synthesis tool according to [1].

- 4) Evaluation of the tool, identifying and including possible improvements.

- 5) Detailed documentation of the tool.

It is important to note that it has not been possible to use the implementation model as input due to the lack of an automatic tool to apply the transformation rules. Instead, the compiler takes the speci cation model directly. Automating the *Transformational Design Refinement* constitutes a much larger project by itself and would have required a high percentage of this thesis to be completed, hindering the development of the compiler.

## Chapter 2

## Lava vs ForSyDe

This chapter is aimed at comparing Lava and ForSyDe, two DSLs (*Domain Specific Languages*) embedded in Haskell. The comparison was made at the initial stage of the thesis, as a means of acquiring a picture of the previous work in the Functional Programming and Hardware Description eld, in order to hopefully reuse earlier design techniques and to provide ForSyDe's compiler with state-of-the-art features. Thus, at the time of writing this comparison the compiler was not yet designed.

During the comparison, the reader will get familiar with the important concept of *Embedded Compiler*. Furthermore, by the end of the chapter he (or she) will ...

- ... be able to understand the problems related to represent circuits in a purely functional programming language such as Haskell.

- ... hopefully have acquired a valuable background in the Hardware design and Functional Languages eld along with an up-to-date view of the previous work related to this thesis.

## 2.1 Introduction

The complexity of electronic designs has tremendously risen during the past two decades which, together with the Industry's exigency of extremely short time-to-market periods have made RTL-level tools no longer t nowadays circuit design requirements. Thus, there has been a natural move to a higher level of abstraction known as *System Level Design*.

The two most commonly-used RTL-level HDLs (Verilog and VHDL) are far too verbose and concrete to cleanly give a general view of a complex system. Therefore, new languages are needed to provide a solution for the aforementioned problems. Among other approaches which require creating a new programming language from scratch, the *Embedded Approach* saves the designer having to learn a new syntax and makes possible to reuse all the existing tools (i.e. compilers, interpreters ...) surrounding the *host language*.

Furthermore, the expressiveness of declarative languages such as Haskell seems to suit the abstraction level of *System Level Design* [9] and hardware design semantics [8].

During the rest of this chapter, two Haskell-embedded language approaches will be compared: Lava [10] and ForSyDe [7]. The later targets synchronous systems in general (that is, systems in which a single global clock is used<sup>1</sup>), while the rst speci cally describes synchronous hardware (a concrete type of synchronous system after all) and is the most mature of the two.

## 2.2 Design flow

Lava and ForSyDe were independently developed by the Swedish universities of Chalmers and KTH.

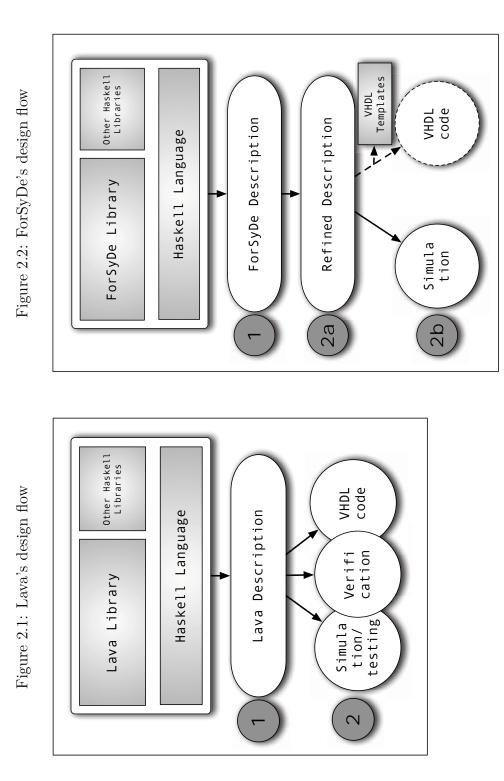

Figures 2.1 and 2.2 contain diagrams describing the simpli ed design flow to be followed when modelling with Lava and ForSyDe. As it will be later seen, the flow is quite similar to the traditional compilation model of a generalpurpose programming language.

It is easy to suspect that both Lava and ForSyDe follow a similar approach, sequentially divided in two stages:

- 1) The designer models a circuit in Haskell, making use of the Lava or ForSyDe libraries.

- 2) The obtained model is automatically processed by a compiler in order to attain di erent goals: simulation, testing, veri cation and translation to a less abstract HDL (e.g. VHDL) directly synthesizable to hardware. The di erent flavours of this stage are known as *Interpretations* in Lava and *Implementation Mappings* in ForSyde. In the rest of this chapter I will refer to them with the wider spread term: *backends*. The details of these backends will be described in next section.

<sup>&</sup>lt;sup>1</sup>ForSyDe supports as well a *multi-rate model* by using *multi-rate interfaces*, able to connect di erent synchronous sub-domains working at di erent clock rates.

11

This stage slightly di ers depending on the language used, being more complex, and potentially more likely to include optimizations in the case of ForSyDe, due to the application of *Design Transformations*.

For SyDe has a strong formal base which allows the designer to work at a highly abstract functional level. The abstraction level is lowered<sup>2</sup> by applying *Transformation Rules* to the provided hardware descriptions. That is captured in gure 2.2 as the transition from 2a to 2b.

The internal details of ForSyDe's *Refinement* are out of the scope of this chapter but is worth to mention that the *Transformation Rules* can be divided in *semantic preserving* and *design decisions*. The later ones change the semantics of the model and thus, its application must be supervised by the designer.

## 2.3 Backends

As it was mentioned previously, Lava is in a more mature state than ForSyDe, having a whole set of tools surrounding it.

On the other hand, ForSyDe only currently supports simulation by direct execution of its Haskell models<sup>3</sup>. Even with that, a *template system*, in which every library function has a preassigned VHDL template, has been already planed and a few prove-of-concept examples [1, Chapter 6] back it as a promising approach.

As of the time of writing this thesis, Lava has three available backends:

• Simulation and random testing. A circuit simulation is carried out by interpreting each component of its structure<sup>4</sup>.

In addition, Lava allows to test properties of a design on random data through a language which is highly inspired in QuickCheck [12].

QuickCheck is as well embedded in Haskell and has been developed independently of the Lava system. That makes it suitable of being used for other purposes than testing circuit properties. Indeed, QuickCheck has been successfully employed in many other projects and could certainly be integrated into ForSyDe if desired.

<sup>&</sup>lt;sup>2</sup>ForSyDe currently lacks an automatic tool for this purpose and transformations need to be applied manually. Either the case, [1] proves it would not only feasible but quite straight-forward to implement.

$<sup>^{3}\</sup>mathit{Zero-delays},$  circuit feedback loops without delays, are forbidden in ForSyDe and thus cannot be simulated.

<sup>&</sup>lt;sup>4</sup>Zero-delays are only permitted when performing a *constructive* simulation by using simulateCon, see Lava s documentation [11] for details.

#### 2.4. LANGUAGE FEATURES

• Verification. Lava is able to generate a logical formula representing the circuit. That formula, along with properties dened by the designer, are given to an external theorem prover which can prove or disprove their validity.

Despite how promising veri cation can seem at rst sight, there is a wellknown underlying theoretic limitation within First Order Logic which makes it semi-decidable<sup>5</sup>. Furthermore, First Order Logic veri cation is computationally expensive (a NP-complete problem) and usually the prover has to be helped by splitting proves in smaller ones.

Fortunately random testing is still at hand and, although it does not answer the validity question, it can be good enough in most of the cases.

Nevertheless, theorem provers can give an answer about the validity of many circuit properties, being especially valuable in critical design parts<sup>6</sup>. As opposed to simulation and random testing, validation provides certainty over circuit properties. Thus, it is more desirable but frequently more di cult to apply.

• **RTL-level language generation**. In order to synthesize a design to hardware, Lava includes a VHDL backend. As it will shown in the next section, such kind of translation is quite straight-forward to achieve in Lava due to the way in which circuits are internally represented. ForSyDe opts for more-behavioural semantics making the translation more di cult to implement.

## 2.4 Language features

Both Lava and ForSyDe can be used to describe synchronous circuits<sup>7</sup>. The functional paradigm invites to model circuits as functions which receive signals as arguments, process them and nally return them or forward them to other functions. Furthermore, higher-order types allow having functions (circuits)

<sup>&</sup>lt;sup>5</sup>Any valid theorem can be proven but invalid clauses are not always identi ed.

<sup>&</sup>lt;sup>6</sup>Intel designers surely regret not making extensive use of formal veri cation methods in an earlier stage. Famous bugs as the Pentium<sup>®</sup> s FOOf [13] and FDIV [14], could probably have been avoided by applying formal methods. Nowadays Intel makes use of the *Forte Verification Environment* [15], currently based on *reFLect* [16], and formerly on FL [17], two functional programming languages.

<sup>&</sup>lt;sup>7</sup>ForSyDe also allows having synchronous subsections working at di erent clock rates, the so-called *synchronous sub-domains*. However, those domains are generated during the *Refinement* stage, which means they cannot be included in the initial hardware description or *Specification Model*.

as rst-class citizens, permitting to combine and nest them in an elegant and intuitive way.

Thus, a hardware model in both Lava and ForSyDe can be viewed as an interconnected set of functions which interact and process signals.

A signal in ForSyDe is de ned with the following recursive algebraic type.

```

data Signal a = NullS | a :- Signal a

```

It is worth to note that

• Signals are represented using a *data stream* metaphor. Its de nition is isomorphic to a Haskell list without syntactic sugar (i.e. the surrounding box brackets [] and interspersed commas).

A similar de nition can be found in Hawk [18], a Haskell-embedded DSL aimed at microprocessor design. Unfortunately the development of the language seems to be dead at the moment of writing the present thesis.

- Signals are polymorphic. The fact that signal can contain values of any type makes them flexible and provides them with abstraction capabilities.

- Following the signal/data-stream metaphor, it is natural to process signals in the same way as lists. In fact, ForSyDe provides higher order functions similar to the Haskell broadly-used list traversers map, zipWith, ...

- The lack of encapsulation of the signal type (i.e. its de nition is not hidden to the programmer) makes it really flexible but as it will be later discussed, it does not permit embedded compilation to other representations such as VHDL.

On the other hand, a signal in Lava is more complex than a stream of values, and is hidden to the programmer through an abstract data type.

```

newtype Signal a = Signal Symbol

```

The de nition of Symbol is not public, and the phantom type parameter a is used as a means to provide a type safety layer for signals.

A signal in Lava hiddenly represents the internal structure of the circuit:

"Instead of implementing signals as streams of booleans, we implement it as a datatype which explicitly keeps track of which gates were used to construct it" [11, section 1.6].

That has three immediate implications

14

#### 2.4. LANGUAGE FEATURES

1) A circuit description in Lava is unavoidably and deliberately structural<sup>8</sup>. On the other hand, ForSyDe is inherently structural as well<sup>9</sup>, but the representation of signals as streams allows the designer to describe systems in a more behavioural manner if required.

For that reason, it can be said that ForSyDe stands on a higher abstraction level. As a drawback, processing the netlist of a circuit is potentially much harder to achieve.

2) A component-wise signal eases the task of processing, translating and transforming a circuit (i.e. simulation, veri cation, translation to a di erent target language ...), permitting to include a translator within the language library.

This technique (known as *Embedded Compiling* [20]) has been successfully used in many other speci c domains such as databases [21], music composition [22] and image processing [23].

3) A circuit is naturally represented as a graph, whereas the closest data structure directly o ered by Haskell is a tree through the use of *algebraic types*.

In order to represent the structure of a circuit and to avoid in nite recursion problems related to circuit loops, Lava o ers two solutions: Monads (currently discarded) and Observable Sharing which will be described later on.

Among other di erences, it should be remarked how both languages make use of Haskell characteristics. Lava makes an elegant use of type classes whereas ForSyDe's programming style is closer to the one used by a generalpurpose Haskell programmer:

- Curry ed functions are used in ForSyDe while Lava uses an uncurry ed style.

- ForSyDe makes use of higher order functions and polymorphic signals which aids reusability. Furthermore, a ForSyDe description consists of a network of cooperating processes joined together through *process constructors* which isolate computation and communication. Each constructor has the capability of using a di erent computational model if desired [24].

<sup>&</sup>lt;sup>8</sup>Part of the Lava team has proposed another imperative behavioural language called *Flash* [19].

<sup>&</sup>lt;sup>9</sup>A model in ForSyDe is presented as the result of connecting di erent processes.

On the other hand, instead of o ering traditional higher order functions (in the sense of data processing callbacks), Lava o ers circuit combinators such as serial and parallel composition. Unfortunately, even if the Lava's signal type is polymorphic, only monomorphic Int and Bool signals can be used in practice<sup>10</sup>.

• The functions o ered by the ForSyDe library follow Haskell's philosophy and naming scheme (e.g. mapSY, zipWithSY, scanlSY ...).

#### 2.4.0.1 Layout-oriented Lava: Xilinx-Lava

Throughout the rest of this thesis the term *Lava* will refer to the main branch of the HDL designed in Chalmers university, also known as *Chalmers-Lava*. However, Satnam Singh, one of the Lava researchers developed a layoutoriented branch of the language, known as *Xilinx-Lava*, which is aimed at describing circuits for implementation of Xilinx's Virtex family of FPGAs [25].

As opposed to *Chalmers-Lava*, *Xilinx-Lava* provides a combinator library to build circuits in a way which allows controlling the nal layout of the FPGA (i.e. how the FPGA blocks are allocated and interconnected) without losing Lava's elegance. So much so that it beats traditional HDLs when it comes to optimizing floorplanning [26].

Due to its layout capabilities, *Xilinx-Lava* is unavoidably less abstract than *Chalmers-Lava* and, unfortunately, as its name clearly indicates, is specific to Xilinx's technology.

### 2.4.1 Representing a circuit in a pure functional language

Hardware design with functional languages has been a matter of research for many years. Its history is neatly summarized by paper [27], which is de nitely recommended to read in order to acquire a deeper background in functional HDLs. More speci cally, the problem of representing a circuit in a pure functional programming language has been addressed and extensively discussed for more than 20 years, mainly by O'Donnell [28, 29, 30, 31, 32, 33].

"The problem is that circuits are finite graphs - but viewing them as algebraic (lazy) data types makes them indistinguishable from potentially infinite regular trees." [31]. In other words, there is no way to directly detect feedback loops within a circuit if an algebraic type is chosen to represent it.

<sup>&</sup>lt;sup>10</sup>The encapsulation of the signal type in addition to the aforementioned type-safety layer only allows Int and Bool signals to be created and propagated. That ensures type correctness and saves the trouble of having to add typechecker to the embedded compiler.

#### 2.4. LANGUAGE FEATURES

In order to solve that problem, there are four main alternatives: *explicit labeling, monads, observable sharing* and *host language transformations*.

### 2.4.1.1 Explicit labeling

This method was proposed by O'Donnell in [29]. In order to prepare the circuit for later traversing, the designer explicitly chooses a label for each node (component) of the circuit.

The approach has many problems, described by O'Donnell himself later on:

"The use of labeling solves the problem of traversing circuit graphs, at the cost of introducing two new problems.

It forces a notational burden onto the circuit designer which has nothing to do with the hardware, but is merely an artifact of the embedding technique. Even worse, the labeling must be done correctly and it cannot be checked by the traversal algorithms.

Suppose that a specification contains two different components that were mistakenly given the same label. Simulation will not bring out this error, but the netlist will actually describe a different circuit than the one that was simulated. Later on the circuit will be fabricated using the erroneous netlist. No amount of simulation or formal methods will help if the circuit that is built doesn't match the one that was designed." [33]

### 2.4.1.2 Monads

This approach was initially adopted and later discarded by the creators of Lava. The labels of the circuit are uniquely and automatically generated through a state monad and stored in the signal abstract data type.

It solves the main problems caused by *explicit labeling* but its main drawback is that, by introducing monads, the syntax in which circuits are expressed changes completely<sup>11</sup> making circuit descriptions less intuitive for the designer.

Furthermore, feedback cannot longer be expressed by means of equational recursion (because of the loss of local naming), and *loop*, a special monadic combinator is required. Again, O'Donnell analyzed the disadvantages of this approach and justi ed why it was not included in his functional HDL: Hydra [35]

"there are two disadvantages of using monads for labeling [..] The first problem is that monads introduce new names one at a time, in a sequence of nested scopes, while Hydra requires the labels to come into scope recursively,

<sup>&</sup>lt;sup>11</sup>Monads have long been one of the biggest learning barriers for Haskell [34], being deeply confusing for the newcomers.

all at once, so that they are all visible throughout the scope of a circuit definition.[..] A more severe problem is that the circuit specification is no longer a system of simultaneous equations, which can be manipulated formally just by 'substituting equals for equals'. Instead, the specification is now a sequence of computations that —when executed— will yield the desired circuit. It feels like writing an imperative program to draw a circuit, instead of defining the circuit directly." [33]

An alternative to Monads: Arrows Arrows [36] are a computation abstraction similar to Monads. Furthermore, Arrows are more general than Monads and are semantically closer to a circuit since they are often introduced from the perspective of stream processors.

Contrary to Monads, they o er combinator primitives which can be targeted at parallel stream processing. Hughes and Paterson even suggested to use Arrows to simulate synchronous circuits [37, 38], nonetheless, no Haskellembedded HDL has so far made use of them.

Arrows are not covered by the Haskell standard. However, GHC (*Glasgow Haskell Compiler*) o ers a notation extension [37] which provides extra syntactic sugar to treat Arrows in a similar way as Monads. The same result can be achieved by preprocessing the code with the compiler-independent *Arrows bundle*.

Even with its semantical advantages, Arrows are prone to su er the same syntactic problems as Monads since they make use of a very similar notation and a *loop* xpoint combinator is still required to express feedback within the circuit.

#### 2.4.1.3 Observable Sharing

This is the currently preferred approach in Lava [31].

The method consists in using references<sup>12</sup> (pointers) to represent the nodes within the graph structure of the circuit (like it would naturally be done in an imperative language). Then, during the graph traversal, loops are detected by comparing the reference of current node against the one of every visited node, whose reference must have been properly saved in advance.

In order to perform such equality comparison, the language needs to be extended with a side-e ecting operation known as  $unsafePerformIO^{13}$ .

<sup>&</sup>lt;sup>12</sup>References are only implicitly used within the signal ADT and are transparently handled for the programmer. Making the reference comparison explicit would constitute a di erent solution known as *Pointer Equality*.

<sup>&</sup>lt;sup>13</sup>All current up-to-date Haskell implementations o er this feature.

#### 2.4. LANGUAGE FEATURES

Observable Sharing allows to design circuits using recursive equations, without the drawbacks of explicit labeling nor the inconvenient monadic syntax. As a tradeo , Haskell needs to be extended into a language which violates referential-transparency, making equational reasoning unsound.

Furthermore, the programmer needs to be aware of such extension since it a ects the way in which connections are shared by the di erent components of the circuit.

#### 2.4.1.4 Host language transformations

The *host* language (Haskell in this case) is preprocessed in order to add the node labels.

As result of the translation an equivalent circuit description is obtained, with correct automatically-added labels, not prone to designer errors, without side-e ects<sup>14</sup> nor unsuitable monad notation.

As it can be suspected, this approach entails the extra e ort of parsing the language and translating it, loosing the pleasant reusability of machinery expected from an embedded language. Furthermore, supporting the full language syntax can be an enormous task and could make the resulting tool di cult to maintain.

The advantages of the embedded language approach, in and of themselves normally questioned [39], are reduced. Syntax reusability would be the only remaining advantage, not being clear if a stand-alone language (as opposed to embedding) would be preferable.

However, a subtle transformation of Hydra was carried out by O'Donnell [33] by making use of TH (*Template Haskell*).

TH [40] is a Haskell extension that provides type-safe (and type-aware) compile-time meta-programming. In his paper, O'Donnell makes use of TH as a macro system to automate the node labeling of the circuit.

Contrary to other popular macro systems, not only is TH type-safe but also gives parsing and AST data structures for free. That allowed O'Donnell to forget about parsing and code his translator as a simple compiler backend, avoiding an otherwise tremendous e ort.

Nonetheless, O'Donnell's approach su ers from various problems:

• **Obfuscation**. As result of preprocessing, the original design is obfuscated and di cult to understand at rst sight.

<sup>&</sup>lt;sup>14</sup>The translated code is pure but it could be said that the original description includes side-e ects anyway, implicitly carried out by the translation.

- **GHC-specific**. Template Haskell is not part of the Haskell standard [3] and is only currently supported by GHC. Nevertheless, GHC is the current *de facto* reference Haskell compiler.

- Host language limitations The publicly available Hydra/TH implementation is very limited and does not support the full feature set of Haskell (not even lambda abstractions are supported). Of course, TH supports the whole Haskell standard and Hydra could be extended to supported. However this shows that supporting it would have made the host language transformations more di cult to implement.

- Maintainability. The dependency on an experimental tool as TH and the wide scope of its use in this approach (traversing the full Haskell AST) makes Hydra/TH di cult to maintain. As a matter of fact, the latest Hydra/TH public version available is outdated at the moment of writing this thesis due to changes in the API of TH.

## 2.5 Lava and ForSyDe in practice

The general characteristics of ForSyDe and Lava have been so far discussed and compared. Even with that, it is di cult to get an overall impression of both languages without having a look at a practical example.

As it was previously stated, ForSyDe is aimed at designing synchronous systems in general, being synchronous hardware just an example of such systems. However, for comparison purposes, a hardware design example (a simple bit adder) was picked from the Lava tutorial [41].

Here is a half adder design in Lava.

```

halfAdd :: (Signal Bool,Signal Bool) -> (Signal Bool,Signal Bool)

halfAdd (a,b) = (sum, carry)

where sum = xor2 (a,b)

carry = and2 (a,b)

```

And here is the full adder, making use of the de nition of halfAdd.

```

fullAdd :: (Signal Bool,(Signal Bool,Signal Bool))

-> (Signal Bool,Signal Bool)

fullAdd (carryIn, (a,b)) = (sum, carryOut)

where

(sum1, carry1) = halfAdd (a, b)

(sum, carry2) = halfAdd (carryIn, sum1)

carryOut = xor2 (carry1, carry2)

```

Lava can *interpret* (i.e. analyse) the model in three di erent ways.

• Simulating it

```

> simulate fullAdd (high,(low,high))

(low,high)

```

• Verifying certain properties. For instance, this property is aimed at checking that the adder is commutative. It is out of scope to explain the details of how this is internally done.

```

prop_c (c, (a,b)) = ok

where out1 = fullAdd (c, (a, b))

out2 = fullAdd (c, (b, a))

ok = out1 <==> out2

```

The property can be easily validated from a Haskell interpreter.

```

> verify prop_c

Proving: ... Valid.

```

• Generating equivalent VHDL code.

```

> writeVhdl "fullAdd" fullAdd

Writing to file "fullAdd.vhd" ... Done.

```

This small example already leads to a few important conclusions

#### • Circuit ports

As it was previously mentioned, Lava circuits are uncurry ed. It can seem unnatural to a Haskell programmer, but this design decision was not arbitrarily made.

An uncurry ed function takes only an argument and thus, it can be encapsulated through typeclass contexts, allowing to treat inputs (outputs) in a uniform way.

The inputs (outputs) admitted by a Lava-interpretable circuit can be defined by induction as the set I where:

$$- \forall s \in Signals. s \in I - \forall i \in I.[i] \in I - \forall i_1, i_2 \in I.(i_1, i_2) \in I - \forall i_1, i_2, i_3 \in I.(i_1, i_2, i_3) \in I \vdots - \forall i_{1,2,...,7} \in I.(i_1, i_2, ..., i_7) \in I$$

Where *Signals* represents the set of all the valid Signal types of Lava and the brackets keep the same meaning as in Haskell.

The above de nition leads to multiple representations of the same circuit input (output). For instance, let's picture the argument of a circuit taking three signals, a Bool signal, followed by an Int signal and lastly a Bool signal.

There are as well, three possible types for the argument of the circuit's function:

- 1) (Signal Bool, Signal Int, Signal Bool)

- 2) ((Signal Bool, Signal Int), Signal Bool)

- 3) (Signal Bool, (Signal Int, Signal Bool))

This feature can be considered redundant and confusing rather than flexible, since it requires a convention on how to structure the circuit inputs. Furthermore it is impossible to avoid the use of nested tuples if the number of input signals is higher than seven. The largest tuple size could be incremented, of course, but it would always remain being nite, and considering the number of inputs required by large VLSI chips

nowadays, it does not seem the best solution.

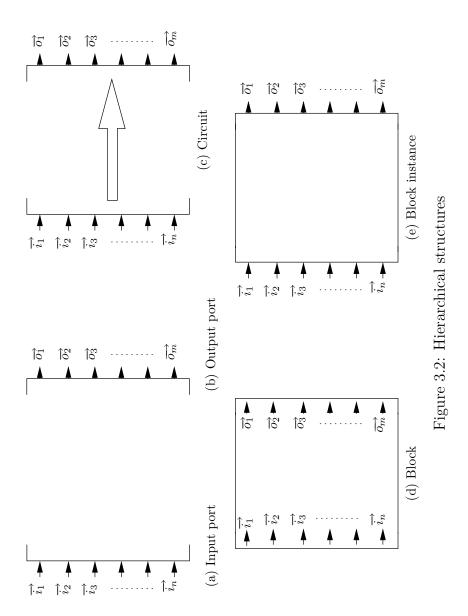

The inputs (outputs) of a circuit are more intuitively expressed with a *port*, in the same way as it is done in traditional HDLs. A good representation for a *port* could be a xed size heterogeneous collection (i.e. a collection whose elements can have di erent types).

Haskell, due to its type strictness and unlike some dynamically-typed functional languages such as Lisp, does not directly support heterogeneous collections. Nonetheless, heterogeneous lists are possible in Haskell as shown by HList [42], a library which relies on common extensions of the language.

*Ports* could be implemented either through heterogeneous collections or a self made ADT, aware of the internal representation of signals.

The price to pay for using *ports* would be some extra verbosity in the circuit descriptions (negligible if the design is big enough) and the e ort of including a typechecker in case the ADT option is chosen (ports, due to their heterogeneous nature, would no longer be able to take advantage of the type safety layer provided by the phantom signal types).

However, *circuit ports* would make the treatment of inputs (outputs) uniform, scalable and intuitive.

22

#### 2.5. LAVA AND FORSYDE IN PRACTICE

#### • Component hierarchy

Reusability and hierarchical structures are two major needs of *System Design*. Lava provides solutions to those needs through mechanisms already available in Haskell. Reusability is achieved by factoring code in functions and hierarchy is o ered by delegating parts of the design to subcircuits (which are functions after all).

In this way, fullAdd makes use of halfAdd without needing to replicate its code and delegating a smaller task to it.

However, the internal representation of the circuit is not aware of such delegation and therefore, the di erent backends are not able to reflect the use of hierarchy in the target language.

That is not a major problem in the case of HDL backends (the components are anyway replicated when the model is synthesized<sup>15</sup>) but it certainly is undesirable in other cases. Suppose that, for instance, a C backend was available. Then code of halfAdd would be replicated in the target source le, making it more di cult to understand than if a subroutine was generated instead. Furthermore, compilation would later lead to a larger binary.

In order to make the backends aware of the circuit hierarchy, the designer would be required to make reusability explicit to Lava. That entails providing component instantiation primitives in the same way it is done in traditional HDLs. As a tradeo , the verbosity of designs would be increased.

Getting back to ForSyDe, an adder could be directly designed as

This behavioural model admits any pair of numbers (in the Haskell sense) as input and calculates their sum and carry (assuming both numbers are unsigned).

The function zipWithSY behaves exactly in the same way as Haskell-Prelude's zipWith. Remember that ForSyDe models signals as data-streams.

Due to its numerical-representation independence, the model accepts numbers of any length and is highly abstract. However, for the same reason, addSY

<sup>&</sup>lt;sup>15</sup>However, the lack of reusability could a ect the behaviour of the synthesizer. For instance, there is no way to split the design in various parts, which can give a hard time to the synthesizer if the circuit is big enough.

is not really useful in practice (at least regarding hardware design): there is not a clear way in which the circuit could be easily synthesizable.

Furthermore, this example would not be fair to Lava, whose fullAdd is proven to be translatable to hardware. A closer approach would be the following

```

halfAddSY :: Signal Bool -> Signal Bool -> Signal (Bool,Bool)

halfAddSY = zipWithSY halfAdd

where halfAdd a b = let sum = a /= b

carry = a && b

in (sum,carry)

fullAddSY :: Signal Bool -> Signal Bool -> Signal Bool

-> Signal (Bool, Bool)

fullAddSY carryIn a b = zipSY sum carryOut

where (sum1, carry1) = unzipSY $ halfAddSY a b

(sum, carry2) = unzipSY $ halfAddSY carryIn sum1

carryOut = zipWithSY (/=) carry1 carry2

```

Note that, even if ForSyDe makes use of curry ed functions, their outputs su er from the same structural redundancy problem as in Lava (i.e. nested tuples).

Furthermore, ForSyDe allows signals to be compound and contain tuples, which can be lifted and unlifted through unzipSY and zipSY, adding even more redundancy and demanding another convention to be followed by the designer.

Due to the previous reasons, ForSyDe could also bene t from the circuit *port* approach. However, the *component hierarchy* remark does not apply in this case, since ForSyDe descriptions are still not synthesizable and thus, not yet representable in terms of components.

## 2.6 Conclusions

The features o ered by functional languages are suitable to embed a *System Level* HDL. Both Lava and ForSyDe follow a similar approach. However, Lava has a whole set of tools surrounding it while ForSyDe only currently o ers simulation. Even though, [1] establishes concrete guidelines on how to automate the re nement stage and the VHDL backend for ForSyDe.

Both Lava and ForSyDe can be considered structural languages. Nonetheless Lava is intrinsically structural due to its internal representation of signals while ForSyDe admits behavioural descriptions of a higher abstraction level if desired. As a drawback, the translation from ForSyDe to other languages (e.g. input for a theorem prover or hardware synthesizer) is potentially more di cult to achieve.

## Chapter 3

## Design of the compiler

The rst part of this chapter describes the compiler's design, including the decisions and arguments which have leaded to it. In advance, it can be said that it follows Lava's embedded compilation model.

The second part of this chapter explains some improvements which were incorporated to ForSyDe in order to overcome the drawbacks of Lava analyzed in chapter 2.

## 3.1 Design alternatives

After studying ForSyDe's background and related work, it was necessary to choose between three design alternatives before starting to implement the compiler:

- 1) **Traditional stand-alone compiler**. This alternative implies coding a full Haskell-to-VHDL compiler from scratch.

- 2) **Customizing an existing compiler**. The Haskell-to-VHDL compiler would be added to an existing tool by incorporating a custom VHDL backend.

- 3) Using an **embedded compilation model**. As it was described in chapter 2, the embedded compilation model involves including the compiler in the language library. This model is used in Lava based on the fact that Lava-signals are component-wise and store a structural description of the circuit.

The third alternative was chosen over the others for various reasons explained in next section.

## 3.1.1 Why an embedded compiler?

There are various reasons for which the embedded compilation model was chosen:

• It is **realistic**.

The time and man-power resources of a master's thesis are very limited.

GHC, the popular Haskell compiler, in its current version (6.6) is composed of around 150.000 lines of Haskell code (or 72 years of estimated one-man full-time dedication)<sup>1</sup>. Even trying to implement a less ambitious compiler, would anyway had been impossible.

A custom backend would obviously had required a much smaller e ort, but it would have been impossible as well. GHC's code generation modules are composed of more than 5.000 lines of code (14 estimated months of one-man full-time dedication).

On the other hand, the embedded approach was expected to be feasible for one person. In fact, the whole compiler is composed of less than 2.000 lines of Haskell code.

#### • Saves unnecessary effort.

The goal of the compiler is to translate ForSyDe speci cations to VHDL. Customizing a backend or coding a full compiler would have allowed to translate any Haskell le (including ForSyDe descriptions in particular).

Such a general translation is not the goal of this thesis. Mapping any Haskell program to VHDL would have been unnecessary and extremely di cult (if not impossible).

#### • Previous success.

The embedded compilation model was adopted from Lava, where it was previously used to build a successful hardware development and veri cation environment.

A previous success always gives a good initial point from were to start working.

### • It is easily **maintainable**.

Using the embedded compilation model, the compiler is included in ForSyDe's Library making it easy to maintain and distribute.

<sup>&</sup>lt;sup>1</sup>measured with the sloccount command, (http://www.dwheeler.com/sloccount/)

#### 3.2. DIFFERENCES WITH LAVA S IMPLEMENTATION

### • It is independent of the internal design of third-party tools.

Modifying an existing compiler to implement a VHDL backend would have caused ForSyDe to depend on a third party tool, making it prone to get outdated by internal design changes in the tool.

## 3.2 Differences with Lava's implementation

Some di erences between Lava and ForSyDe made impossible to simply replicate Lava's compilation model.

Those di erences had to be analyzed and taken into account in order to be able to preserve Lava's approach. The di erences were identi ed in last chapter and fortunately, an appropriate solution was found for each case:

## • ForSyDe already defines a Signal type.

The embedded compilation model requires to use a signal type which stores the structure of the circuit.

However, ForSyDe's library implements the Signal type as a stream of values. Furthermore, the Signal type is not encapsulated (that is, the data type is not hidden to the programmer), making impossible to modify it without causing regressions.

There were two alternatives

- a) Transform the original Signal type of ForSyDe, into an ADT which kept track of the circuit structure, causing a regression.

- b) Create an alternative signal type which fullled the requirements of embedded compiling and which could live together with the old Signal type.

Option b was chosen, mainly because ForSyDe is targeted at design of systems in general not simply hardware. The details about the new signal type are explained in section 3.3.

## • ForSyDe is more behavioural than Lava.

The behaviour of Lava's gates (e.g and, or, xor ...) is hardcoded and cannot be modi ed, which is perfectly natural for a purely structural language.

On the other hand, most of ForSyDe's process constructors are implemented as higher-order functions, which behave in one way or another depending on the function passed as argument. Keeping the structure of the circuit in a the signal ADT was no longer enough to perform the translation to VHDL. In addition, a way to store the body of the functions passed to the process constructors had to be found.

The biggest problem was that an embedded compiler does not have direct access to AST of the host language. The only information it can work with has to be provided by the library in which the compiler is embedded.

One possible solution would have been developing yet another embedded language in which to express the body of those functions. However, it would have implied designing a new sublanguage, with its new syntax, which would had to be learned by the designer.

Instead, inspired by Hydra's implementation [33], it was decided to make use of Template Haskell through a new ADT: HDFun. HDFun is covered in section 3.4.

## • Polymorphism.

Even if the Lava's signal type is polymorphic, only monomorphic Int and Bool signals can be used in practice.

On the other hand ForSyDe's original Signal is polymorphic and so are its process constructors. There is no automatic way to transform every kind of signal value into VHDL code, and thus, the subset of supported ForSyDe signals has to be controlled.

HDPrimType type-class constraints were used in process constructors as way to control the supported signal subset. The details about the HDPrimType typeclass are described in section 3.5.

The next sections give explicit details about how Lava's embedded compilation model was adapted to ForSyDe.

In order to make it more intuitive for the reader. Each section incrementally refers to the speci c changes which were made to mapSY, originally de ned in ForSyDe's Library as:

```

mapSY :: (a -> b) -> Signal a -> Signal b

mapSY _ NullS = NullS

mapSY f (x:-xs) = f x :- (mapSY f xs)

```

Remember that the de nition of Signal is isomorphic to Haskell lists and is de ned as:

```

data Signal a = NullS

| a :- Signal a

```

28

| $\overrightarrow{i}$ | mapSY | $\overrightarrow{O}$ |

|----------------------|-------|----------------------|

|                      | (+1)  |                      |

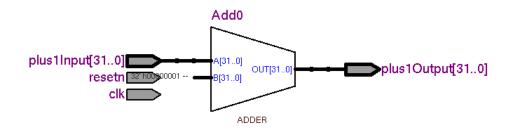

Figure 3.1: *plus1*

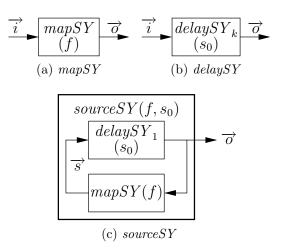

To illustrate how the design mode cations a ect the end-user, the transformations su ered by the original de nition of a simple system will be used as example. plus1 (gure 3.1) is a trivial system which merely adds 1 to its numerical input and returns the resulting value. Its code, using the original ForSyDe Library is:

```

plus1 :: Num a => Signal a -> Signal a

plus1 = mapSY (+1)

```

## 3.3 HDSignal: The Hardware Description Signal

In order to avoid regressions, instead of modifying the original Signal type, an alternative signal type, HDSignal (*Hardware Description Signal*) was introduced.

HDSignal works similarly to signals in Lava. It is an ADT hidden to the user which *secretly* stores the structure of the circuit.

HDSignal makes use of *Observable Sharing* [31] (introduced in chapter 2) to achieve its goal. Understanding the concrete implementation details of *Observable Sharing* requires an advance knowledge of Haskell which is out of the scope of this report. Therefore, HDSignal will simply be treated as an abstract type with unknown implementation.

```

data HDSignal a = ... -- hidden

```

Providing an alternative version of Signal required as well to provide new process constructors, which were initially renamed to avoid name-clashes.

Thus, an alternative de nition of mapSY using HDSignal was created:

```

hdMapSY :: (a->b) -> HDSignal a -> HDSignal b

hdMapSY ... -- hidden implementation

```

plus1 also needed to renamed and modi ed to make use of HDSignals

```

hdPlus1:: Num a => HDSignal a -> HDSignal b

hdPlus1 = hdMapSY (+1)

```

## **3.4** HDFun: the Hardware Description Function

Using the de nition of previous section, hdMapSY takes a standard Haskell function as argument:

hdMapSY :: (a->b) -> HDSignal a -> HDSignal b

However, there is no possible way of generating VHDL code from a (a->b) value. Instead, a new type, HDFun (*Hardware Description Function*), capable of storing the de nition of a function was introduced.

HDFun, contrary to a standard Haskell function, contains a syntax tree thanks to the use of Template Haskell.

## 3.4.1 Introduction to Template Haskell

TH [40] (*Template Haskell*) was previously mentioned in chapter 2. It is a Haskell extension that enables to use compile-time meta-programming. Unfortunately, as it was stated before, TH is only currently supported by GHC.

Meta-programming allows to write programs which manipulate and/or generate other programs. In Template Haskell, that is done by processing the AST (*Abstract Syntax Tree*) of Haskell declarations or expressions.

In the case of HDFuns, Template Haskell gives access to the AST of function declarations, allowing ForSyDe's embedded compiler to translate them to VHDL.

The key abstractions that Template Haskell operates on are Expressions, Declarations, and Types. Fragments of concrete Haskell code can be *lifted* into the meta-world through the use of quasi-quotations. Expression, declaration and type fragments each have their own variation on the quotation syntax:

```

[| expr |] -- lifts a concrete expression

[d| decl |] -- lifts a concrete declaration

[t| type |] -- lifts a concrete type

```

As a result of lifting, the AST of the quoted expression, declaration or type is obtained for later processing.

In order to generate code, Template Haskell provides *splices* which are executed at compile-time and return an AST. GHC automatically merges the resulting AST with the rest of the source code as if the programmer actually wrote it. Informally, it can said that splices work like C macros, but are type-safe, ensuring the generation of correct code.

Splices have their own notation. A splice is written x, where x is an identi er, or (...), where ... is an arbitrary Haskell expression. This use of v overrides its meaning as an in x operator. To be interpreted as an operator, v needs to be surrounded by spaces.

The biggest advantage of using Template Haskell is the reutilization Haskell syntax, which saves the designer from learning a new embedded language. As a drawback, TH introduces syntax extensions (quotes and \$) which anyway require certain learning, and makes ForSyDe GHC-dependent.

## 3.4.2 HDFuns in practice

With the introduction of HDFun, the type of hdMapSY changes to

hdMapSY :: HDFun (a->b) -> HDSignal a -> HDSignal b

which is still quite similar to the original de nition of mapSY. Furthermore, *plus1* needs as well to be readapted:

```

hdPlus1 :: Num a => HDSignal a -> HDSignal a

hdPlus1 = hdMapSY doPlus1

where doPlus1 = $(mkHDFun [d| doPlus1 :: Num a => a -> a

doPlus1 a = a + 1 |])

```

The internal HDFun of hdPlus1 is generated at compile-time as follows:

- 1) The declaration of doPlus1 is lifted to its AST thanks to the enclosing brackets ([| ... d|]).

- 2) Its AST is processed by a splice in which the mkHDFun constructor function creates the HDFun.

It is worth to note that doPlus1 is de ned as

doPlus1 a = a + 1

instead of simply

doPlus1 = (+1)

due to the limitations of mkHDFun.

Those limitations are:

- The number of formal parameters in the function must equal its number of arguments.

- The signature of the function is mandatory and only one de nition clause is admitted.

- Pattern matching is only supported with literals, variables and the wildcard \_ pattern. No other kind of pattern matching is allowed.

- where clauses are not supported.

• The only valid expressions are: variables, constructors, in x operations (excluding in x constructors and sections), if, case and the expressions resulting form their combination. let, lambda abstractions, and the rest kinds of expressions are not supported.

These limitations can be considered excessive. However, they provide a su cient initial functionality. Thanks to the use of TH, this limitations can be easily overcome by extending the supported Haskell subset of HDFun (see A for details).

# 3.5 Controlling polymorphism: the HDPrimType type class

As it was previously said, there is no automatic way to transform every Haskell type into VHDL, and thus, the subset of supported ForSyDe signals has to be controlled somehow.

Indeed, only instances of HDPrimType (*Hardware Description Primitive Type*) can be handled by the compiler. Currently, only Int and Bool instantiate HDPrimType.

The process constructors have to reflect that limitation. For that reason, a HDPrimType constraint was introduced in each of its parameters. In the case of hdMapSY, its type changes to:

```

hdMapSY :: (HDPrimType a, HDPrimType b) =>

HDFun (a->b) -> HDSignal a -> HDSignal b

```

That means as well that *plus1* can no longer support numerical signals in general. A concrete type has to be specified so that the compiler can chose an adequate VHDL representation.

```

hdPlus1 :: HDSignal Int -> HDSignal Int

hdPlus1 = hdMapSY doPlus1

where doPlus1 = $(mkHDFun [d| doPlus1 :: Int -> Int

doPlus1 a = a + 1 |])

```

The implementation details of HDPrimType are not signi cant. However, it is worth to note that it shares certain similarities with Haskell's Data.-Typeable.Typeable class. Thus, HDPrimType can be considered a particular implementation of dynamic types.

## 3.6 Integration with ForSyDe's Library

So far, the original mapSY function has been renamed to hdMapSY and modi ed to include all the requirements of the embedded compiler.

Both functions use di erent types but are intended to attain a similar goal. Therefore, it would be desirable to make them share the same name (mapSY), without causing a name-clash.

Thanks to a Haskell extension called MPTC [43] (*Multi Parameter Type Classes*), it is possible to make them share mapSY as their name:

```